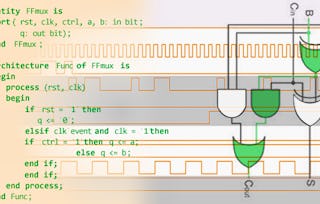

This comprehensive, hands-on course equips learners with the practical skills needed to design real hardware using SystemVerilog. Through a structured four-module progression, you will master the fundamentals of RTL development starting from basic modules and data types, moving into advanced constructs like structs, enums, and generate blocks, and culminating in the design of a fully functional digital calculator. Each module includes hands-on exercises, simulation-based assignments and guided coding practice

SystemVerilog Tutorials: Hardware Design & Verification

SystemVerilog Tutorials: Hardware Design & Verification

Instructors: Emmanuel Ezeuko

Access provided by Leidos

Gain insight into a topic and learn the fundamentals.

Intermediate level

Recommended experience

5 hours to complete

Flexible schedule

Learn at your own pace

What you'll learn

Design synthesizable SystemVerilog modules and integrate combinational and sequential logic to form complete digital subsystems.

Implement an Arithmetic Logic Unit (ALU) capable of performing core operations and basic arithmetic for calculator functionality.

Develop a finite state machine (FSM) to control complex system modes (calculator modes), user inputs, and operation sequencing.

Simulate, verify, and debug SystemVerilog designs to ensure functionality of the full calculator system.

Skills you'll gain

- Data Structures

- Design

- Software Design

- Computer Engineering

- Programming Principles

- Verification And Validation

- Test Engineering

- Analysis

- Electronic Systems

- Application Specific Integrated Circuits

- Embedded Systems

- Systems Design

- Data Synthesis

- Hardware Design

- Simulation and Simulation Software

- Process Optimization

Tools you'll learn

Details to know

Shareable certificate

Add to your LinkedIn profile

Assessments

1 assignment

Taught in English

Recently updated!

February 2026

See how employees at top companies are mastering in-demand skills

There are 3 modules in this course

Offered by

Why people choose Coursera for their career

Felipe M.

Learner since 2018

"To be able to take courses at my own pace and rhythm has been an amazing experience. I can learn whenever it fits my schedule and mood."

Jennifer J.

Learner since 2020

"I directly applied the concepts and skills I learned from my courses to an exciting new project at work."

Larry W.

Learner since 2021

"When I need courses on topics that my university doesn't offer, Coursera is one of the best places to go."

Chaitanya A.

"Learning isn't just about being better at your job: it's so much more than that. Coursera allows me to learn without limits."

Explore more from Computer Science

University of Colorado Boulder

Universitat Autònoma de Barcelona

University of Colorado Boulder